DAC 的內(nèi)部電路構(gòu)成無太大差異,一般按輸出是電流仍是電壓、能否作乘法運(yùn)算等進(jìn)行分類。大多數(shù)DAC由電阻陣列和n個(gè)電流開關(guān)(或電壓開關(guān))構(gòu)成。按數(shù)字輸入 值切換開關(guān),產(chǎn)生份額于輸入的電流(或電壓) ��。此外,也有為了改善精度而把恒流源放入器件內(nèi)部的�。DAC分為電壓型和電流型兩大類,電壓型DAC有權(quán)電阻網(wǎng)絡(luò)、T型電阻網(wǎng)絡(luò)和樹形開關(guān)網(wǎng)絡(luò)等;電流型 DAC有權(quán)電流型電阻網(wǎng)絡(luò)和倒T型電阻網(wǎng)絡(luò)等。

ADC的首要技術(shù)目標(biāo)

1. ADC分辨率指輸出數(shù)字量改變一個(gè)最低有用位(LSB)所需的輸入模仿電壓的改變量��。

2. ADC的精度決定于量化差錯(cuò)及體系內(nèi)其他差錯(cuò)之總和����。一般精度目標(biāo)為滿量程的±0. 02% ,高精度目標(biāo)為滿量程的0. 001%�。

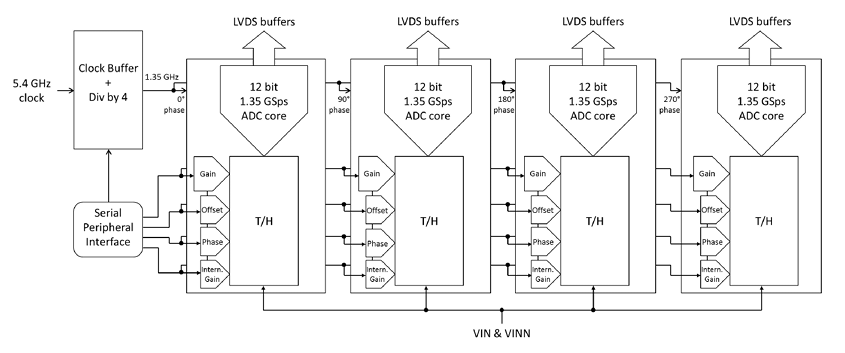

3 .轉(zhuǎn)化速率是指完成一次從模仿轉(zhuǎn)化到數(shù)字的AD轉(zhuǎn)化所需的時(shí)刻的倒數(shù)。積分型AD的轉(zhuǎn)化時(shí)刻是毫秒級(jí)屬低速AD,逐次比較型AD是微秒級(jí)屬中速AD,全并行/串并行型AD可到達(dá)納秒級(jí)��。

4. 量化差錯(cuò)由于AD 的有限分辨率而引起的差錯(cuò),即有限分辨率AD的階梯狀搬運(yùn)特性曲線與無限分辨率AD (抱負(fù)AD)的搬運(yùn)特性曲線(直線)之間的最大偏差�。通常是1個(gè)或半個(gè)最小數(shù)字量的模仿改變量,標(biāo)明為1LSB、1 /2LSB��。

DAC的首要技術(shù)目標(biāo)

1 .分辨率指輸出模仿電壓的最小增量,即標(biāo)明DAC輸入一個(gè)最低有用位(LSB)而在輸出端上模仿電壓的改變量��。

2. 樹立時(shí)刻是將一個(gè)數(shù)字量轉(zhuǎn)化為穩(wěn)定模仿信號(hào)所需的時(shí)刻,也能夠認(rèn)為是轉(zhuǎn)化時(shí)刻�。DA中常用樹立時(shí)刻來描述其速度,而不是AD中常用的轉(zhuǎn)化速率��。一般地,電流輸出DA樹立時(shí)刻較短,電壓輸出DA則較長��。

3 .精度是指輸入端加有最大數(shù)值量時(shí),DAC的實(shí)踐輸出值和理論計(jì)算值之差,它首要包括非線性差錯(cuò)、份額體系差錯(cuò)��、失調(diào)差錯(cuò)����。

4 .線性度在抱負(fù)情況下,DAC的數(shù)字輸入量作等量添加時(shí),其模仿輸出電壓也應(yīng)作等量添加,可是實(shí)踐輸出往往有偏離。

深圳市立維創(chuàng)展科技是EUVIS數(shù)模轉(zhuǎn)換器的代理經(jīng)銷商��,主要提供EUVIS的DAC��、DDS�、DAC等產(chǎn)品�,原裝現(xiàn)貨,價(jià)格優(yōu)勢��,歡迎咨詢

詳情了解EUVIS數(shù)模轉(zhuǎn)換器請(qǐng)點(diǎn)擊:http://m.lunliu2.cn/brand/24.html

更多產(chǎn)品咨詢����,請(qǐng)聯(lián)系我們的銷售代表:0755-83050846 QQ: 3312069749